Zihao Awarded PD Soros Fellowship for New Americans

12 Apr 2016By Lauren Tompkins

Group member Zihao Jiang has been named a member of the 2016 PD Soros Fellows! Text of the announcement is below. Congratulations Zihao!!

Thirty Outstanding Immigrants & Children of Immigrants Each Awarded $90,000 For Graduate School By The Paul & Daisy Soros Fellowships for New Americans

The Paul & Daisy Soros Fellowships for New Americans program announces 2016 Fellows; Fellows reflect accomplishments and diversity of immigrants and refugees in the United States; Launch 2017 Application

April, 12, 2016 (New York) - Today, The Paul & Daisy Soros Fellowships for New Americans, the premier graduate school fellowship for immigrants and children of immigrants, announced their 2016 recipients. The thirty recipients, called “Fellows”, were selected for their potential to make significant contributions to US society, culture, or their academic field, and were selected from a pool of 1,443 applicants. With a two percent acceptance rate, it was the most competitive year in the Fellowship’s history.

Daisy M. Soros and Paul Soros (1926-2013) founded the Fellowship program in 1997, which has awarded more than 550 Fellowships over its 18 year history. The couple, both Hungarian immigrants, has contributed $75 million to the organization’s charitable trust.

In addition to receiving up to $90,000 in funding for the graduate program of their choice, each new Fellow joins the prestigious community of recipients from past years, which includes US Surgeon General Vivek Murthy, leading Ebola researcher Pardis Sabeti, Aspiration founder Andrei Cherny, Oscar health insurance co-founder Kevin Nazemi and over 535 other New American leaders.

“The Fellows are from all different countries and socio-economic and religious backgrounds, and they have come to the United States in a myriad of ways – but they all bring excellence to the table,” said Craig Harwood, who directs the Fellowship program. “They demonstrate that immigrants, regardless of their background, continue to be a critical part of our nation.”

The 2016 Fellows, who are 30 or younger, come from a range of socio-economic backgrounds, and are all naturalized citizens, green card holders, DACA recipients, or the children of immigrants. Their backgrounds reflect the diversity of recent immigrants and refugees in the United States. Those who were born abroad hail from Bangladesh, Burma, Canada, China, the Dominican Republic, Egypt, Germany, India, Iran, Israel, Mexico, Nigeria, Pakistan, Saudi Arabia, the United Arab Emirates, and the United Kingdom.

Here is a sampling of their stories: Veronica Manzo, who was born in California to Mexican parents in a family of farmworkers, has performed brain cancer research that was published in Nature. Goran Micevic, who grew up in war-torn Yugoslavia, was wrongly arrested and held by secret police at the age of 12, and moved to the United States to attend Iowa State University. He is now a National Cancer Institute Fellow and MD/PhD student at Yale University. Jenna Nicholas, whose parents are of Middle Eastern and European descent, is studying business at Stanford and is the founder and CEO of an impact investment firm.

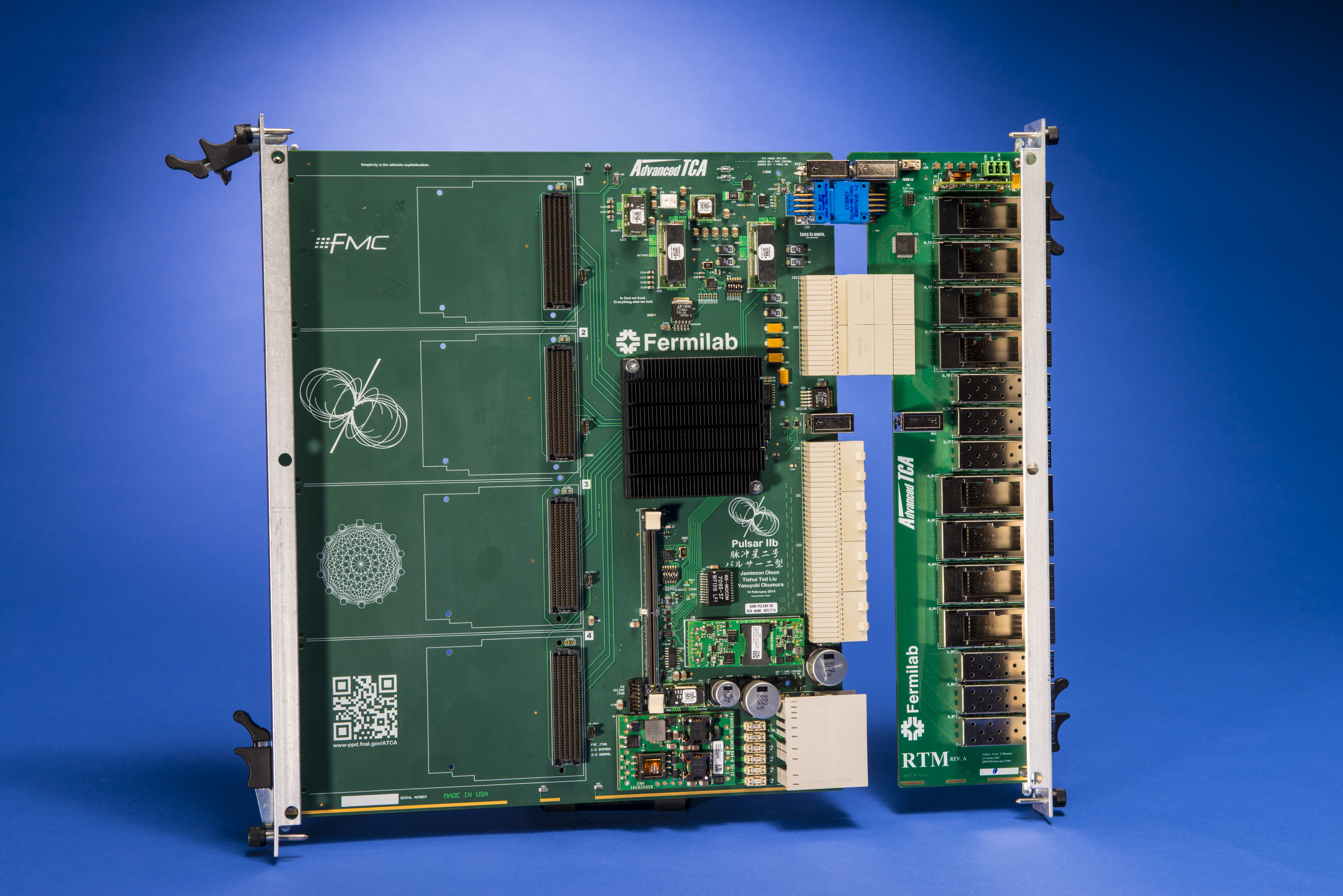

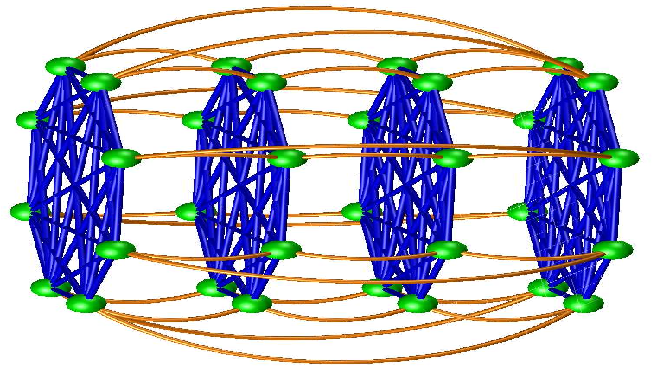

Denisse Rojas Marquez, the first undocumented student to attend Icahn School of Medicine at Mount Sinai, was born in Mexico City and co-founded a Pre-Health Dreamers organization for undocumented students. Zihao Jiang’s father, who lived in poverty while working as a school teacher during the Cultural Revolution in China, could have only dreamed that his son would reach the highest levels of the United States university system. Zihao is now performing research at the Large Hadron collider at CERN as a PhD student at Stanford. Shadi Gaheri, who was one of the first women to direct campus theater at her university in Tehran, came to the United States at the age of 23 to pursue a career as a theater director; she is now at the Yale School of Theater. Suan Lian Tuang, who was born in Burma and immigrated to the US at the age 16, is pursuing an MD/PhD in chemistry at Harvard and MIT.