| Signature: |                 | Last name (print):                      |                                                |                               |

|------------|-----------------|-----------------------------------------|------------------------------------------------|-------------------------------|

| EE486—A    | dvanced C       | rithmetic                               |                                                | The solution of the solutions |

| 110100001  | 111111111111    | Midterm Exam                            |                                                |                               |

| 1. For     | RN and RP, shov | v the final rounded results in th       | e following cases:                             |                               |

|            | s Exponent      | Fraction                                | Guard S                                        |                               |

|            | 0 00011111      | 111111111111111111111111                | 1 0                                            |                               |

|            | 0 111111110     | 111111111111111111111111111111111111111 | 1 1                                            |                               |

|            | 1 111111110     | 111111111111111111111111111111111111111 | $\begin{bmatrix} 1 & 1 \\ 1 & 0 \end{bmatrix}$ |                               |

|            | 0 00000000      | 111111111111111111111111111111111111111 | 1 0                                            |                               |

|            |                 |                                         |                                                |                               |

|            |                 |                                         |                                                |                               |

|            |                 |                                         |                                                |                               |

|            |                 |                                         |                                                |                               |

|            |                 |                                         |                                                |                               |

|            |                 |                                         |                                                |                               |

| [          | s Exponent      | Fraction                                | Comment                                        |                               |

|            |                 |                                         |                                                |                               |

| RN         |                 |                                         |                                                |                               |

|            |                 |                                         |                                                |                               |

|            |                 |                                         |                                                |                               |

|            |                 |                                         |                                                |                               |

|            |                 |                                         |                                                |                               |

|            |                 |                                         |                                                |                               |

|            |                 |                                         |                                                |                               |

|            |                 |                                         |                                                |                               |

|            |                 |                                         |                                                |                               |

| Г          |                 |                                         |                                                |                               |

| _          | s Exponent      | Fraction                                | Comment                                        |                               |

| RP         |                 |                                         |                                                |                               |

| KP         |                 |                                         |                                                |                               |

|            |                 |                                         |                                                |                               |

| L          | ı               |                                         |                                                |                               |

|            |                 |                                         |                                                |                               |

|            |                 |                                         |                                                |                               |

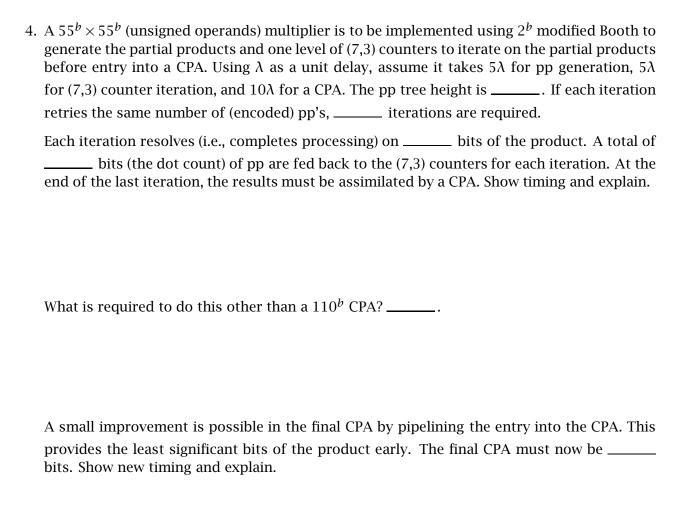

| 2. | In recent years, there have been a number of Stanford theses (Santoro, Song, Bewick) showing the advantages of various counter configurations. |                                                                          |  |

|----|------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|--|

|    | (a)                                                                                                                                            | Show a (7,3) and a "(4,2)" counter made from GSA's—i.e., (3,2) counters. |  |

|    |                                                                                                                                                |                                                                          |  |

For the middle bits (h = 28), show the reduction of the partial produce tree to two inputs to a CPA. Using counters

- (a) (7,3) —reduce to 3 and use a single CSA to input to the CPA

- (b) "(4,2)"

- (c) (3,2)

Approximately how many counters are required for each, and how many serial CSA delays before entry to the CPA?

EE 486 Midterm

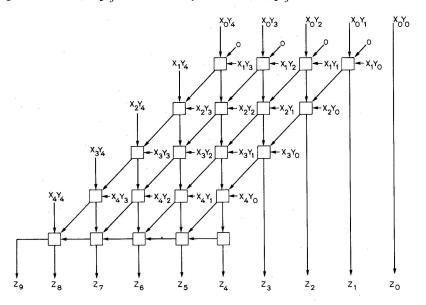

3. In an effort to simplify multiplication layout and control, linear arrays of adder cells have been suggested [Pezaris, 1971]. Here, each cell is a full adder that adds a pp bit  $x_iy_j$  with the sum output from  $x_{i-1}y_{j+1}$  and carry from  $x_{i-1}, y_{j-1}$ .

Each adder has a delay of 2 units. For this array approach, the delay to form a product of  $48 \times 48$  operands is \_\_\_\_\_\_. The approach uses \_\_\_\_\_ adder cells.

A Wallace tree would use \_\_\_\_\_\_ levels of CSA and have an overall delay of \_\_\_\_\_\_ (for CPA, assume r=3, CLA implementation). Show computation. Approximately how many CSA are required in the Wallace approach? \_\_\_\_\_.

Can the linear array be used with Booth? Explain.

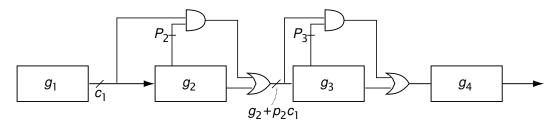

5. Carry skip adders are a type of inexpensive adder where a ripple carry within a group is combined with a simple group bypass, based on a group propagate signal. So we have:

Suppose it takes 2 units of delay to form a bit sum or bit carry. Each AND and OR gate has one unit delay. It would take 32 delay units for a 16-bit adder to generate either the worst sum or carry. **Note:** the worst case may be any of the sum bits as well as the carry.

- (a) In a 16-bit adder with 4 groups of 4 bits each, the (worst case) delay is \_\_\_\_\_. Show this path.

- (b) Suppose we now allow variable bit size groupings. If we retain the structure drawn above (each group must have at least one bit), what is the optimum bit grouping?

g1 \_\_\_\_\_

g2 \_\_\_\_\_

g3 \_\_\_\_\_

g4 \_\_\_\_\_

This gives \_\_\_\_\_

delay (worst case).

(c) Now suppose we vary the allowable number of groups, but the structure must still follow the figure. Find a better delay than above. For your solution:

What is the number of groups? \_\_\_\_\_.

What is the assignment of bit sizes to each group? \_\_\_\_\_.

What is the resultant (worst case) delay? \_\_\_\_\_.