|                                          | Semiconductor Industry Roadmap |      |                     |       |  |  |  |

|------------------------------------------|--------------------------------|------|---------------------|-------|--|--|--|

|                                          |                                |      |                     |       |  |  |  |

| Semiconductor Technology Roadmap (2001)  |                                |      |                     |       |  |  |  |

| Year                                     | 2001                           | 2004 | 2007                | 2013  |  |  |  |

| Technology generation (nm)               | 130                            | 90   | 65                  | 32    |  |  |  |

| Wafer size (mm)                          | 300                            | 300  | 300                 | 450   |  |  |  |

| Defect density (per m <sup>2</sup> )     | 1356                           | 1356 | 1356                | 1116  |  |  |  |

| $\mu P$ die size (mm <sup>2</sup> )      | 310                            | 310  | 310                 | 310   |  |  |  |

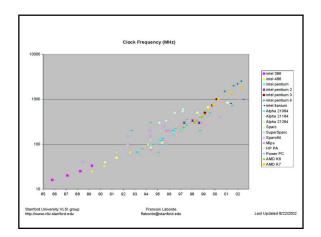

| Chip Frequency (MHz)                     | 1767                           | 4000 | 6700                | 19350 |  |  |  |

| MTx per Chip (Microprocessor)            | 276                            | 552  | 1204                | 4424  |  |  |  |

| MaxPwr(W) High Performance               | 130                            | 160  | 190                 | 251   |  |  |  |

| Computer Architecture & Arithmetic Group | 2                              |      | Stanford University |       |  |  |  |

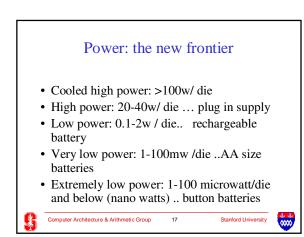

| type              | energy        | time                                               | power        |

|-------------------|---------------|----------------------------------------------------|--------------|

|                   | capacity      |                                                    |              |

| recharage<br>able | 10,000<br>mAh | 50 hours<br>(10-20%<br>duty)                       | 400mw-<br>4w |

| 2xAA              | 4000 mAh      | <sup>1</sup> ⁄ <sub>2</sub> year (10-<br>20% duty) | 1-10 mw      |

| button            | 40mAh         | 5 years<br>(always on)                             | 1uw          |

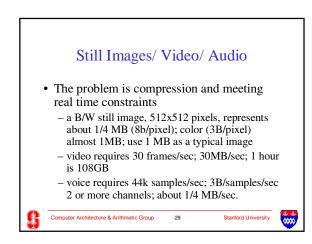

- Includes video, audio, 3 D graphic imaging, as well as subsidiary functions such as music (composition and rendering), voice recognition, handwriting rec., animation

- Closely coupled to the display / presentation technology (raster line or pixel density, audio speaker fidelity / range)

28

Stanford University

0000

Computer Architecture & Arithmetic Group

## Summary

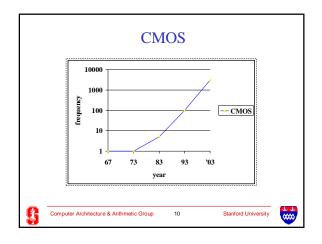

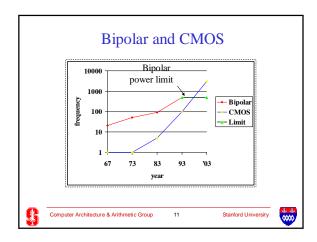

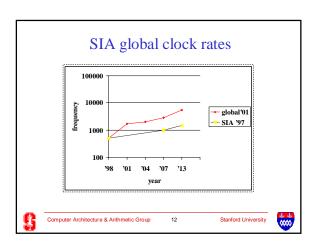

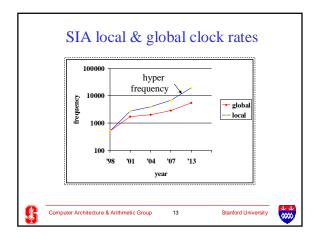

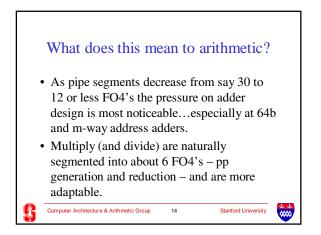

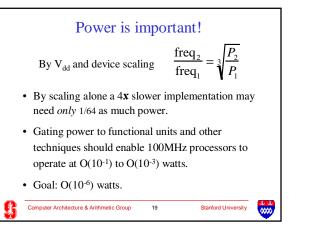

- Processor design with deep sub-micron (f < 90nm) technology offers major advantages: 10x speed or 10<sup>-6</sup> power and 100x circuit density. Indeed, SIA projections have consistently underestimated the future.

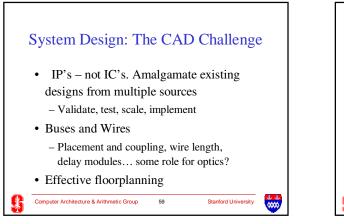

- But the real challenge is in system not processor design: new system products and concepts, ip management and design tools.

61

Stanford University

4000

Computer Architecture & Arithmetic Group