## Lecture #12: The Memories..., ahh the Memories...

Paul Hartke Phartke@stanford.edu Stanford EE121 February 19, 2002

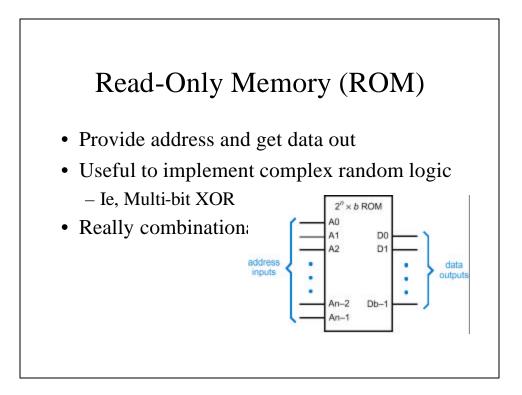

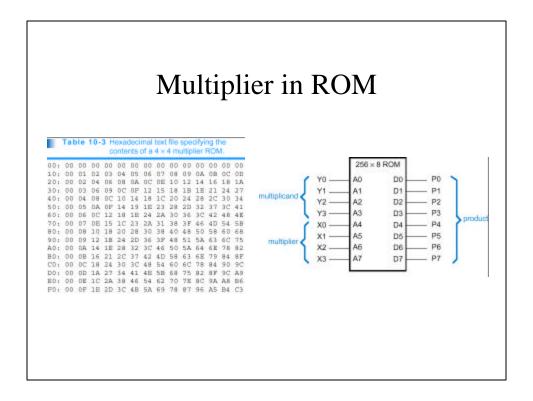

## Memories in Digital Design

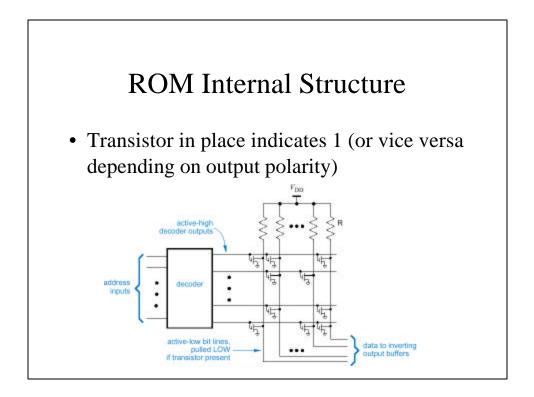

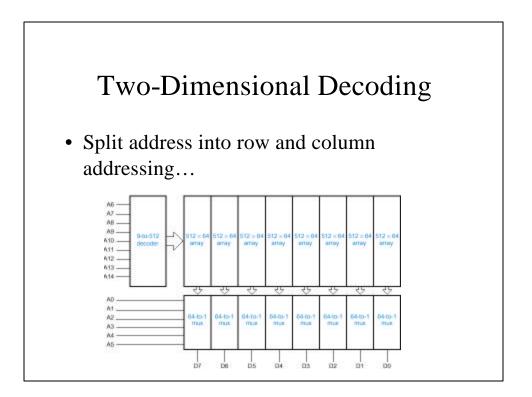

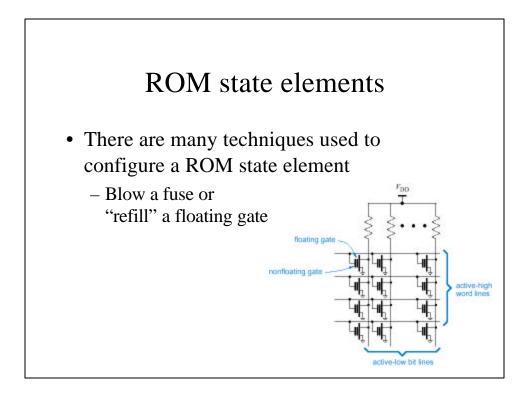

- Special Idiom in logic design.

- Different types of lookup tables (LUTs)

- Same basic idea we have seen in the FPGA architecture.

## Two Port & Dual Port

- What if you had two ports for reading and writing and accessed the same location.

- What happens? Depends on the device

- Old data, new data, bad data...

- If you have separate clocks then basis of circuit to pass data between clock domains...

| Parameters 📓 Core Ove | rview 🔛 Contact                                   |                                                            |                            |                                   |

|-----------------------|---------------------------------------------------|------------------------------------------------------------|----------------------------|-----------------------------------|

| logi <del>CŘ</del> RE | Dual Port Block Memory                            |                                                            |                            |                                   |

| ADDRA DOUTA           | ComponentName:<br>                                | -                                                          |                            |                                   |

|                       | Width A 16<br>Width Bt 16                         | Valid Range: 1.255                                         | Depth A: 16<br>Depth B: 16 | Valid Range: 2.3276               |

|                       | - Port A Options -                                |                                                            |                            |                                   |

| - DINA REDUK          | Configuration:<br>99/18 Mode:                     | Read And Write     Read And Write     Read And Write       | C Read Before Posts        | C Read Only<br>C No Read On White |

| CLKA<br>ADDRB DOUTB   | - Port B Options -<br>Configuration:<br>With Mode | <ul> <li>Read And Write</li> <li>Read And Write</li> </ul> | C Write Only               | C Read Only                       |

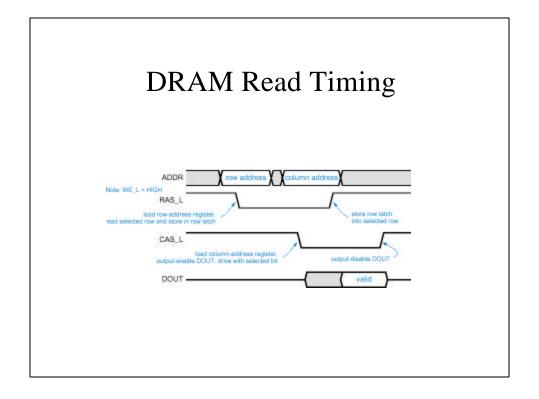

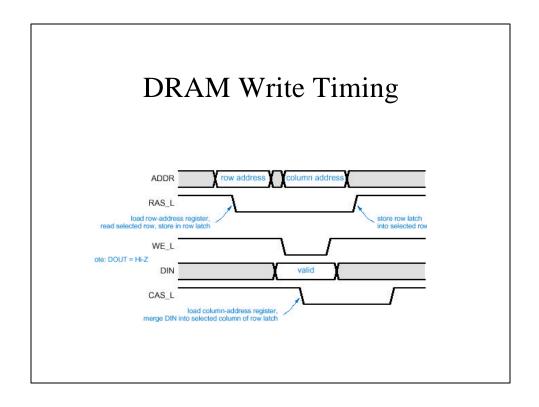

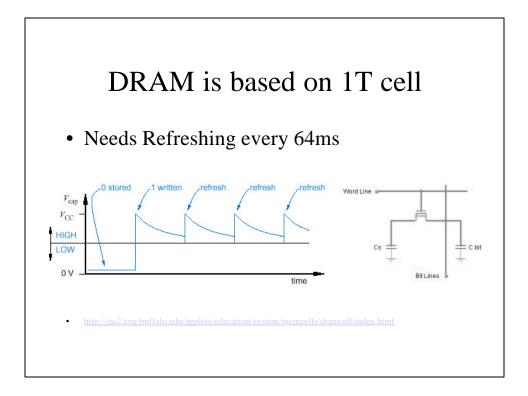

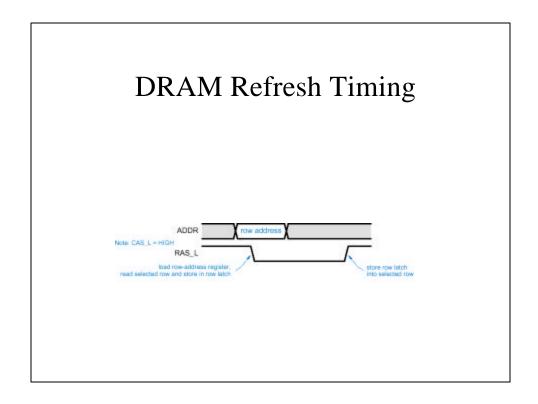

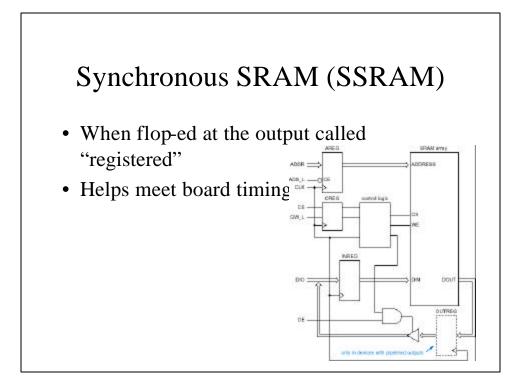

- SRAM like structure but present the row and column addresses separately and sense amplifier on bit lines detects output data.

- Can be Synchronous and have registered outputs.

- The one on the XSA-100 board is http://www.hynix.co.kr/datasheet/pdf/dram/(2)HY57V281620A(L)T-LPDE