## Lecture #4: Programmable Logic Structure

Paul Hartke Phartke@stanford.edu Stanford EE121 January 17, 2001

## FPGAs

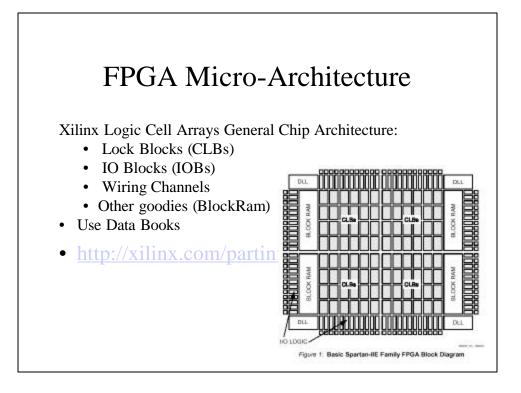

• Field Programmable Gate Arrays have a more general structure but based on these primitives.

| _                                |                        | ng   |          | n          | fo       |    |          |           |           |     |           |

|----------------------------------|------------------------|------|----------|------------|----------|----|----------|-----------|-----------|-----|-----------|

|                                  |                        | -6   |          |            |          |    |          |           |           |     |           |

|                                  |                        |      |          |            |          |    |          |           |           |     |           |

| http://xilinx.com                | m/nai                  | rtii | nfc      | $\sqrt{d}$ | sO       | 05 | n        | -lf       |           |     |           |

|                                  | <u>n pa</u>            |      |          | J U        | 00       | UJ | •P       | <u>ar</u> |           |     |           |

| • Use this info to               | alles                  | cti  | im       | ate        | հ հ      | OV | v f      | 201       | t d       | AC  | i σ1      |

|                                  | gues                   | su   |          | an         |          | UV | V I      | as        | ιu        | US. | igi       |

| (( 1 1 199                       |                        |      |          |            |          |    |          |           |           |     |           |

| "should" run.                    |                        |      |          |            |          |    |          |           |           |     |           |

| "should" run.                    |                        |      |          |            |          |    |          |           |           |     |           |

| "Should" run.                    | delines                |      |          |            |          |    |          |           |           |     |           |

|                                  | delines<br>Speed Grade |      | 3        |            | 2        |    | 1        | -         | 09        | -   | 06        |

|                                  |                        |      | 3<br>Max |            | 2<br>Max |    | 1<br>Max |           | 09<br>Max |     | 08<br>Max |

| CLB Switching Characteristic Gui | Speed Grade            |      |          |            |          |    | -        |           | · · · ·   |     |           |

| CLB Switching Characteristic Gui | Speed Grade            |      |          |            |          |    | -        |           | · · · ·   |     |           |

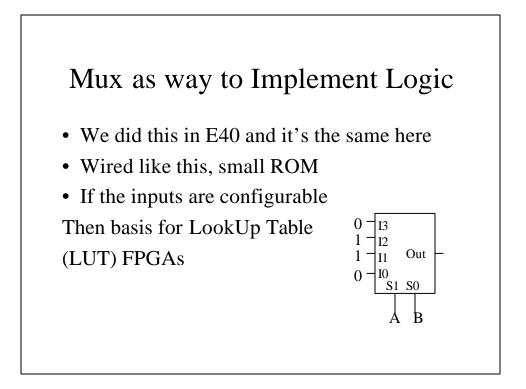

## Understand FPGA Architecture

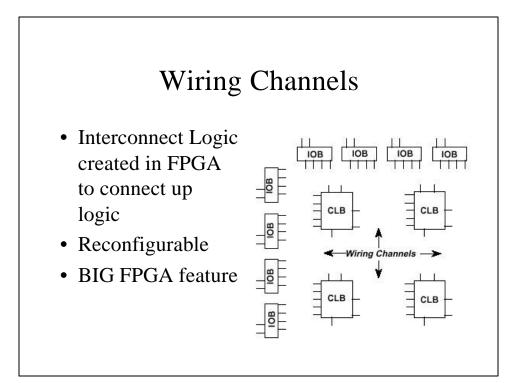

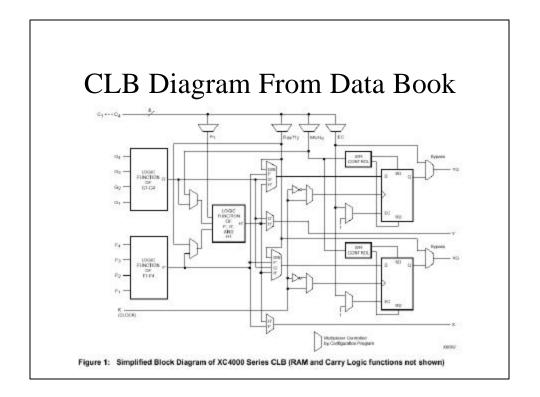

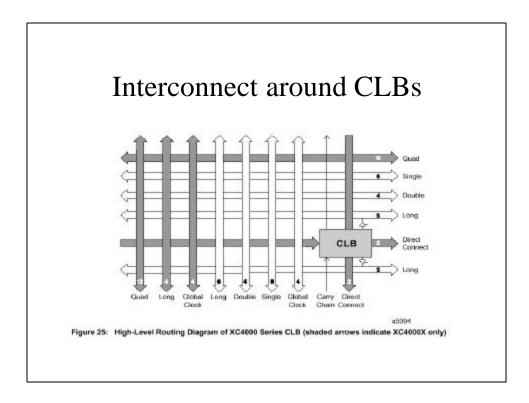

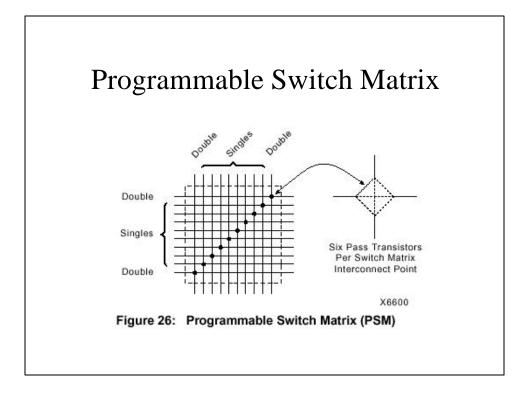

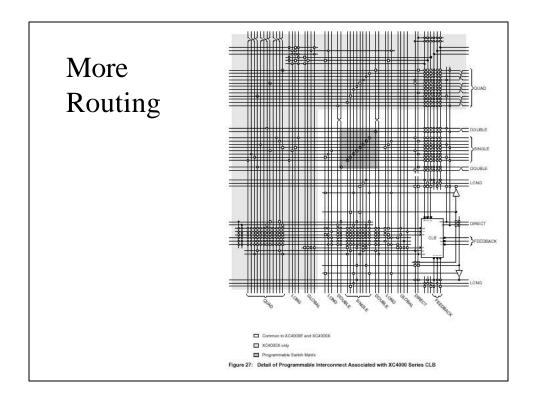

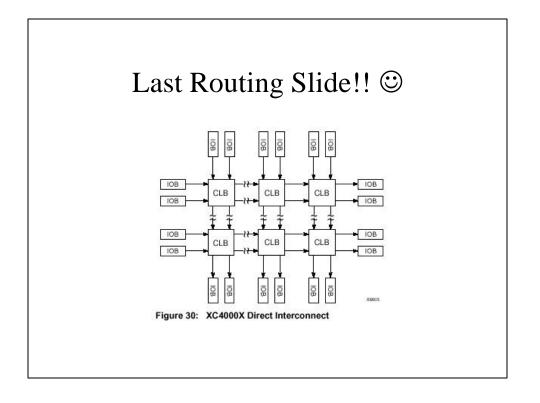

- Look up table (LUT) based with fixed and *limited* routing resources.

- So logic is cheap (consider 4 input XOR in VLSI) but wires are very expensive.

- FPGAs are manufactured in the same chip fabs as "high performance" ASICs based on standard CMOS. The tradeoff is easy of design vs performance.

- Often a good tradeoff.