## Lecture #2: Digital Logic Implementation

Paul Hartke Phartke@stanford.edu Stanford EE121 January 10, 2001

## What is inside these chips?

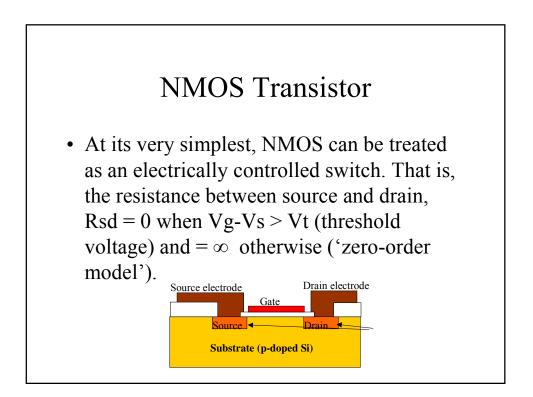

- Transistors of course!!!!

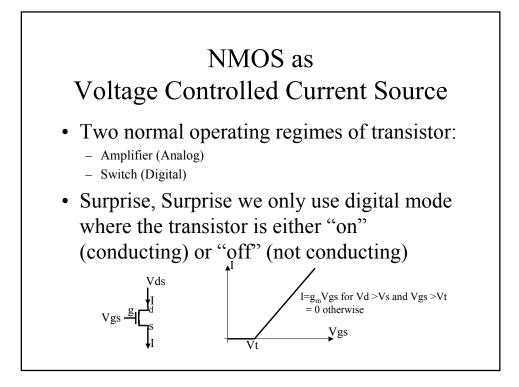

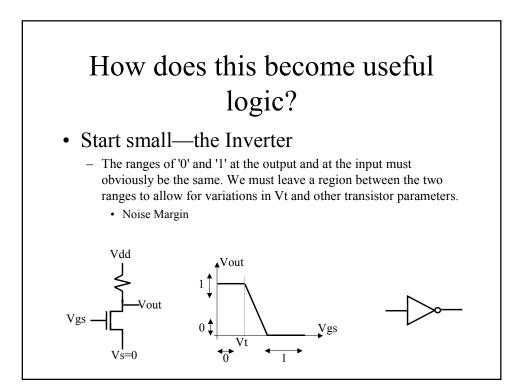

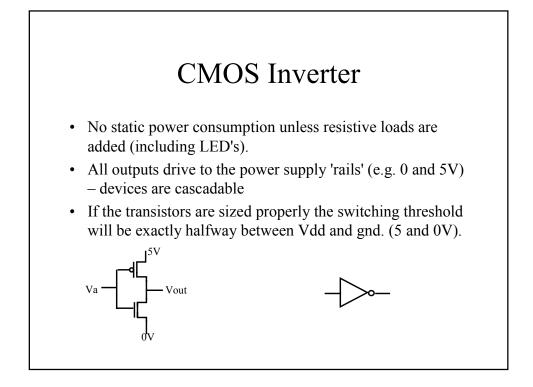

- In lab 2 you will deal with bipolar transistor circuits (Transistor-Transistor Logic, TTL) as well as CMOS transistor circuits. TTL is more robust, usually faster, but more "expensive" and power hungry. During the last 20 years MOS circuitry has become fast enough for nearly all applications. That is all the detail we need for EE121.

## Power Calculation

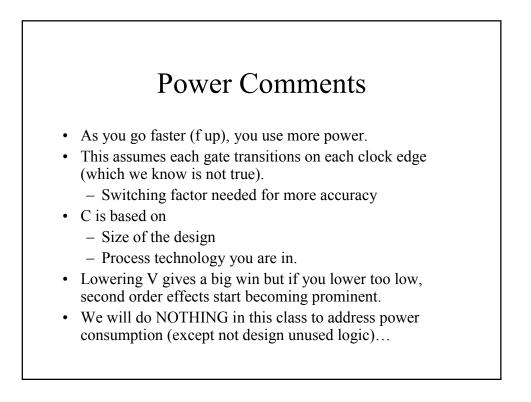

- For each transistor how much power is being consumed?

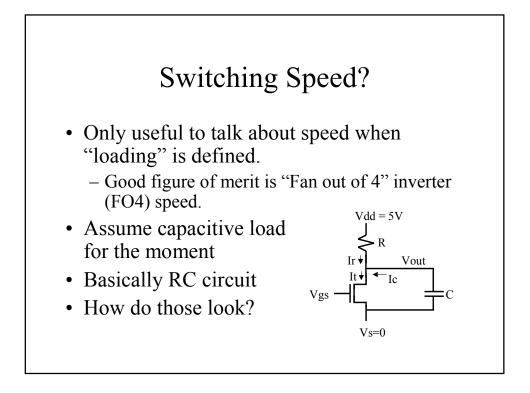

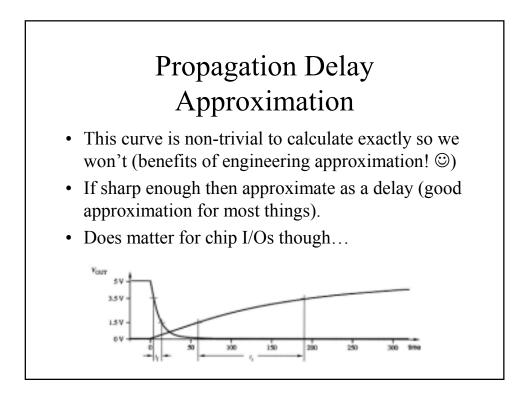

- If it is only driving a capacitive load, then we can approximate that all the power is consumed in the act of switching. It is nontrivial to calculate the power via the resistance of the on transistor so use the output capacitance.

- Power to charge/discharge a cap:  $\frac{1}{2}CV^2$

- Assume circuit is driven by a clock (one up and one down transition) so it is CV<sup>2</sup> each clock cycle

- If the clock frequency is f, then equation becomes:

## We won't be doing CMOS design in EE121

- Designing with the actual transistors ("full custom design") is very complex and expensive so we won't be doing it (take EE271—it's very good).

- Using discrete components as in E40 leaves a lot of wiring drudgery so we don't want to do that either.

- Field Programmable Gates Arrays (FPGAs) to the rescue!!!!

- They are built from CMOS logic which is why we covered today's material.