|                                                        | Topics for Lecture #9                                        |              |

|--------------------------------------------------------|--------------------------------------------------------------|--------------|

| • Reminder: midte                                      | erm examination $\#1$ next Tuesday starting                  | g at 9:30am. |

| <ul><li>button push p</li><li>pulse stretche</li></ul> | button push detector (continued)<br>processor<br>r           |              |

|                                                        | re for state machine design<br>tions, examples, applications |              |

| October 24, 2002                                       | EE 121: Digital Design Laboratory                            | Lecture 9–1  |

|                                                        | Button input processor                                       |              |

Requirement: output a pulse of duration one clock period in response to each input pulse.

Example of desired behavior.

| CLK |                                                                                                                                  |

|-----|----------------------------------------------------------------------------------------------------------------------------------|

| IN  |                                                                                                                                  |

| OUT |                                                                                                                                  |

|     | ashed pulse corresponds to an ambiguity in the specifications: how this state machine respond to consecutive short input pulses? |

|     | e applications consecutive pulses will not or should not occur, so this ility can be ignored.                                    |

|     |                                                                                                                                  |

|     |                                                                                                                                  |

|                                           | Button input processor (2)                                             |              |

|-------------------------------------------|------------------------------------------------------------------------|--------------|

| State machines and                        | transition/output tables.                                              |              |

|                                           |                                                                        |              |

|                                           |                                                                        |              |

|                                           |                                                                        |              |

|                                           |                                                                        |              |

|                                           |                                                                        |              |

|                                           |                                                                        |              |

|                                           |                                                                        |              |

|                                           |                                                                        |              |

|                                           |                                                                        |              |

| October 24, 2002                          | EE 121: Digital Design Laboratory                                      | Lecture 9-3  |

|                                           | Pulse stretcher                                                        |              |

| Requirement: each i                       | nput pulse produces a 4-clock output pul                               | se.          |

| Example of desired I                      | behavior:                                                              |              |

|                                           |                                                                        |              |

| IN                                        |                                                                        |              |

| OUT                                       |                                                                        |              |

| These specifications output pulses be lon | are also ambiguous: is the output <i>retrigg</i><br>ger than 4 clocks? | gerable? Can |

|                                           |                                                                        |              |

|                                           |                                                                        |              |

|                                           |                                                                        |              |

| October 24, 2002                          | EE 121: Digital Design Laboratory                                      | Lecture 9–4  |

- 0. Specify desired behavior of machine unambiguously (often hardest step).

- 1. Construct state/output table (or draw a state diagram, often preferable).

- 2. Minimize the number of states (optional).

- 3. State assignment: choose state variables and assign values to named states.

- 4. Form transition/output table from state/output table using state values.

- 5. Choose flip-flop type. Answer: D flip-flops

- 6. Construct excitation table (not needed for D flip-flops)

- 7. Derive excitation equations from excitation table.

- 8. Derive output equations from transition/output table.

- 9. Draw logic diagram of next-state logic (or provide equations to CAD tools).

October 24, 2002

- Real time clock: cycle through a sequence of states in a known order. State encodings: binary, BCD = binary coded decimal, Gray.

- Frequency divider: output a period signal at a fraction of input frequency.

- Event counter: increment state each time a signal or Boolean function is true (on rising edge of clock).

- Interval timer: count number of clock pulses between start and stop signals

- Alarm clock: activate an alarm signal at a specified time in the future.

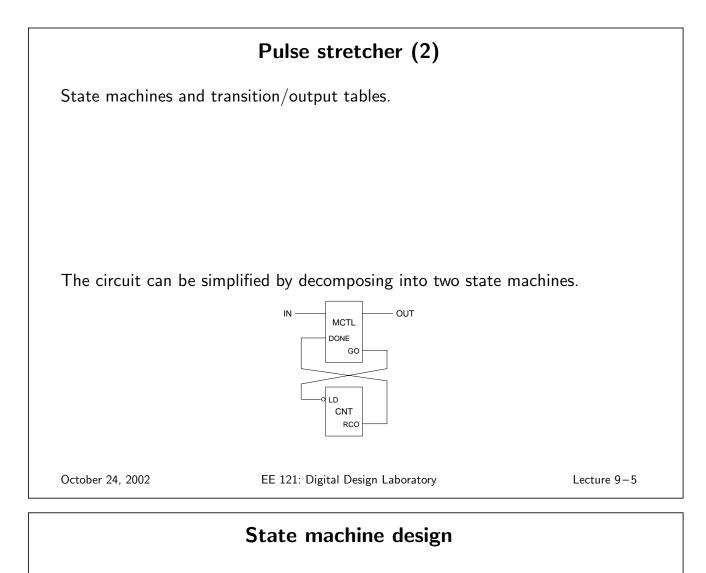

- Delay: activate a timeout signal after a specified number of clock cycles.

October 24, 2002

EE 121: Digital Design Laboratory

Lecture 9-7

October 24, 2002

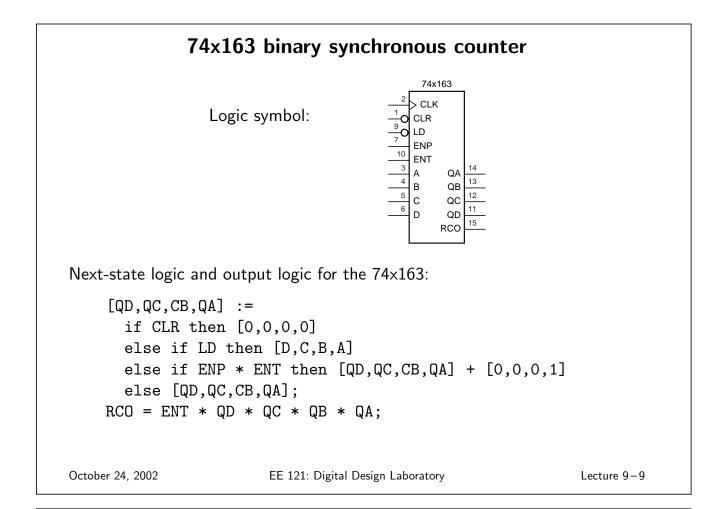

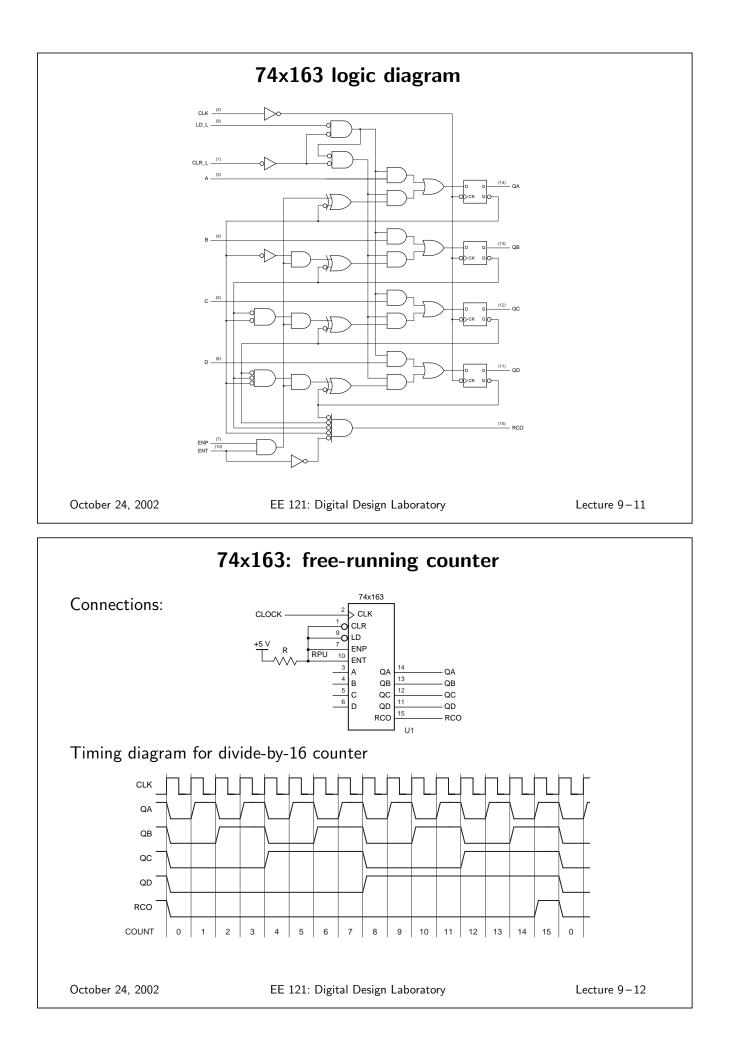

## 74x163 state table

| Inputs |       |      |       |    | Current State |    |    |    | Next State |     |     |     |     |

|--------|-------|------|-------|----|---------------|----|----|----|------------|-----|-----|-----|-----|

| CLR_L  | . LD_ | L EN | IT EI | NP | QD            | QC | QB | Q, | ł          | QD* | QC* | QB* | QA* |

| 0      | х     | x    | 3     | ĸ  | х             | x  | х  | х  |            | 0   | 0   | 0   | 0   |

| 1      | 0     | x    | 3     | ĸ  | х             | х  | x  | x  |            | D   | С   | В   | А   |

|        | 1     | 1    | 0     | х  |               | x  | x  | x  | x          | QD  | QC  | QB  | QA  |

|        | 1     | 1    | х     | 0  |               | x  | х  | х  | х          | QD  | QC  | QB  | QA  |

|        | 1     | 1    | 1     | 1  |               | 0  | 0  | 0  | 0          | 0   | 0   | 0   |     |

|        | 1     | 1    | 1     | 1  |               | 0  | 0  | 0  | 1          | 0   | 0   | 1   | (   |

|        | 1     | 1    | 1     | 1  |               | 0  | 0  | 1  | 0          | 0   | 0   | 1   |     |

|        | 1     | 1    | 1     | 1  |               | 0  | 0  | 1  | 1          | 0   | 1   | 0   |     |

|        | 1     | 1    | 1     | 1  |               | 0  | 1  | 0  | 0          | 0   | 1   | 0   |     |

|        | 1     | 1    | 1     | 1  |               | 0  | 1  | 0  | 1          | 0   | 1   | 1   |     |

|        | 1     | 1    | 1     | 1  |               | 0  | 1  | 1  | 0          | 0   | 1   | 1   |     |

|        | 1     | 1    | 1     | 1  |               | 0  | 1  | 1  | 1          | 1   | 0   | 0   |     |

|        | 1     | 1    | 1     | 1  |               | 1  | 0  | 0  | 0          | 1   | 0   | 0   |     |

|        | 1     | 1    | 1     | 1  |               | 1  | 0  | 0  | 1          | 1   | 0   | 1   |     |

|        | 1     | 1    | 1     | 1  |               | 1  | 0  | 1  | 0          | 1   | 0   | 1   |     |

|        | 1     | 1    | 1     | 1  |               | 1  | 0  | 1  | 1          | 1   | 1   | 0   |     |

|        | 1     | 1    | 1     | 1  |               | 1  | 1  | 0  | 0          | 1   | 1   | 0   |     |

|        | 1     | 1    | 1     | 1  |               | 1  | 1  | 0  | 1          | 1   | 1   | 1   |     |

|        | 1     | 1    | 1     | 1  |               | 1  | 1  | 1  | 0          | 1   | 1   | 1   |     |

|        | 1     | 1    | 1     | 1  |               | 1  | 1  | 1  | 1          | 0   | 0   | 0   |     |

October 24, 2002

EE 121: Digital Design Laboratory

Lecture 9-10

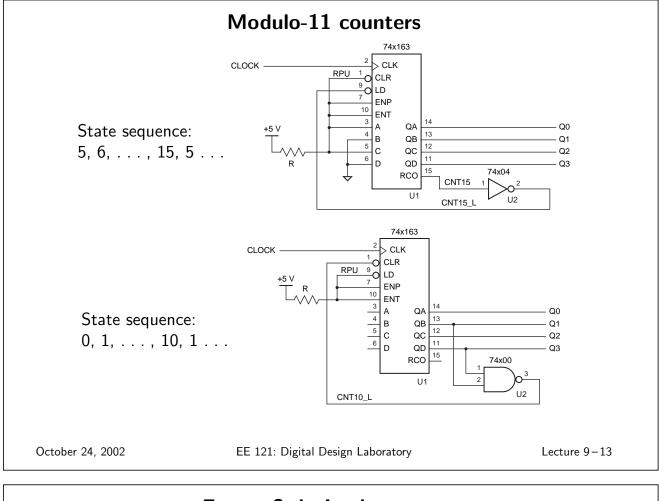

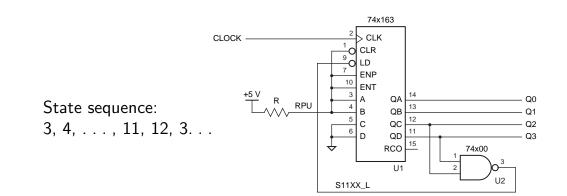

## **Excess-3 decimal counter**

With one 3-input NAND gate, any period between 1 and 16 can be obtained. In fact, any low and high values can be specified.

Drawback of 74x163: counts up only. Use 74x169 for bidirectional counting.