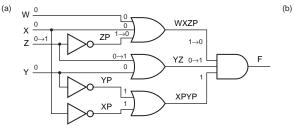

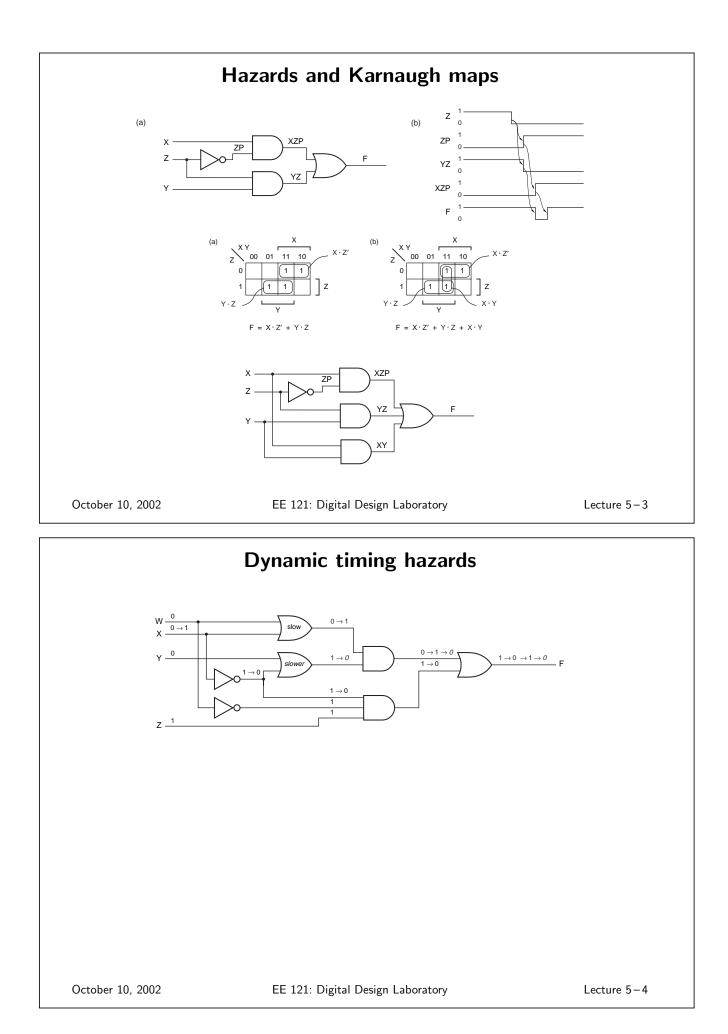

Product of sums: static-0 hazard:

F 0

October 10, 2002

EE 121: Digital Design Laboratory

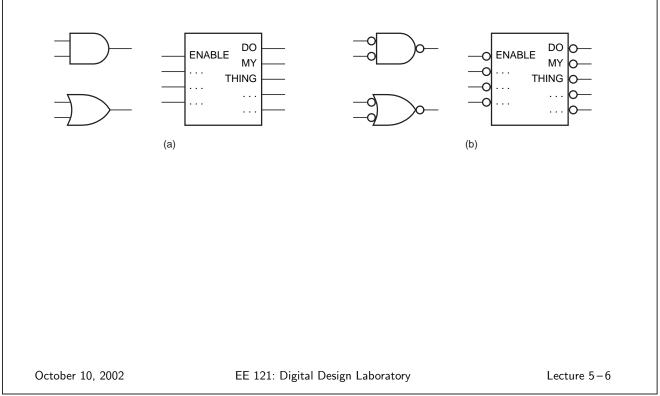

#### Signal names and active levels

Some inputs and outputs are "active" (cause something to happen) when their voltage level is low. These signals are called "active-low."

Most logic circuits contain a mixture of active-high and active-low signals.

One reason: simplest gates (NAND, NOR, NOT) are inverting.

Signal names should when possible indicate the active level of the signal.

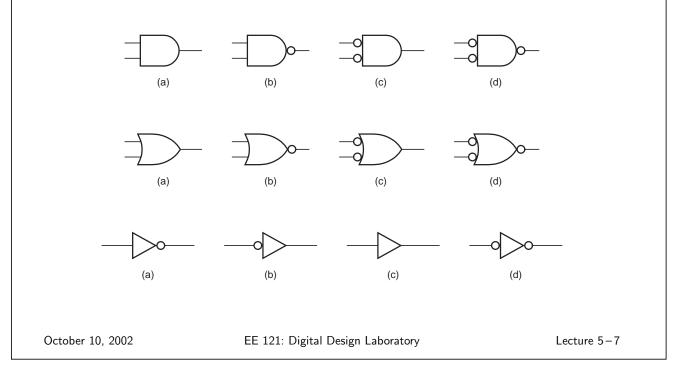

# **Bubbles**

Active-low input and output signals are indicated by bubbles:

## Bubbles (2)

The same conceptual function (AND, OR, NOT) can be implemented by different gates, depending on active level of inputs and outputs.

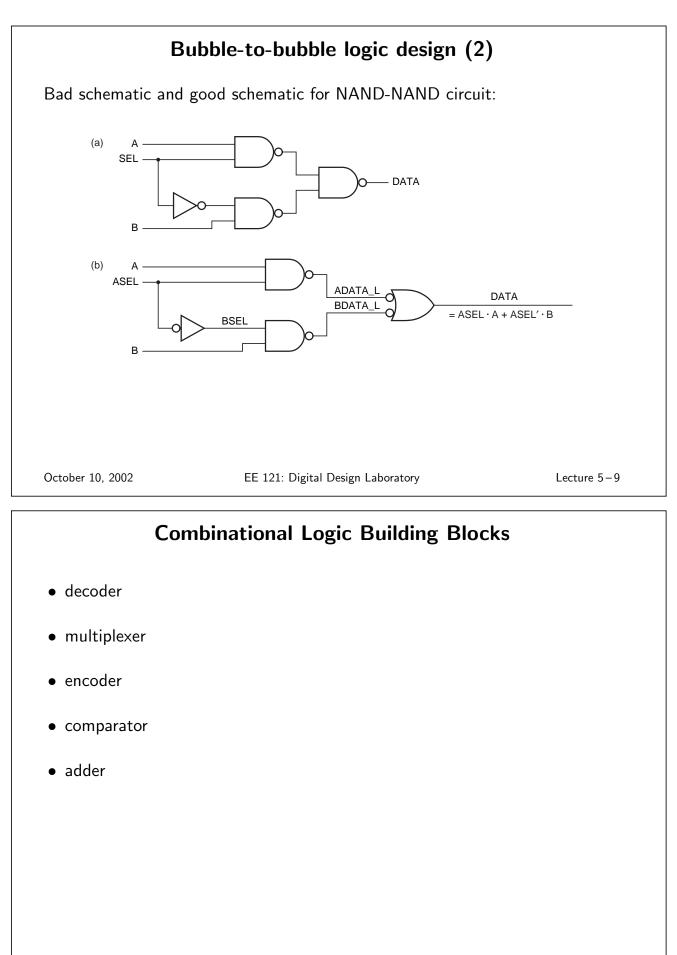

# Bubble-to-bubble logic design

Ideally, active-low signals should connect to bubbles on gates. (We cannot always match active-low signals to bubbles: e.g.,  $Y = A \cdot B'$ .) READY READY GO\_L GO REQUEST REQUEST (a) (b) READY\_L -READY\_L -GO GO\_L REQUEST\_L -REQUEST\_L -C റ (c) (d) READY READY\_L READY\_L GO GO REQUEST\_L REQUEST REQUEST (a) (b) October 10, 2002 EE 121: Digital Design Laboratory Lecture 5-8

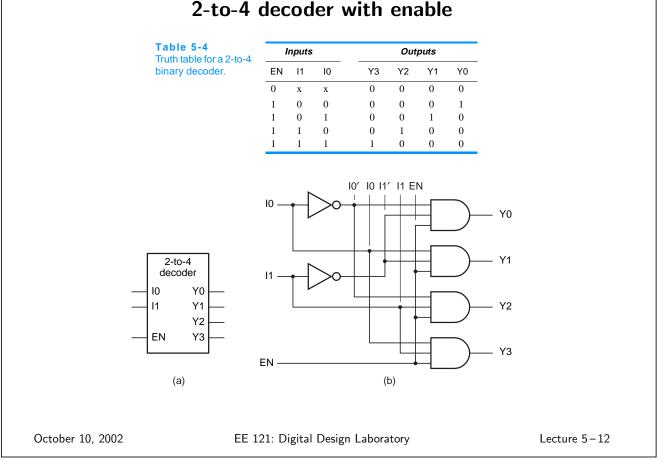

#### 2-to-4 decoder with enable

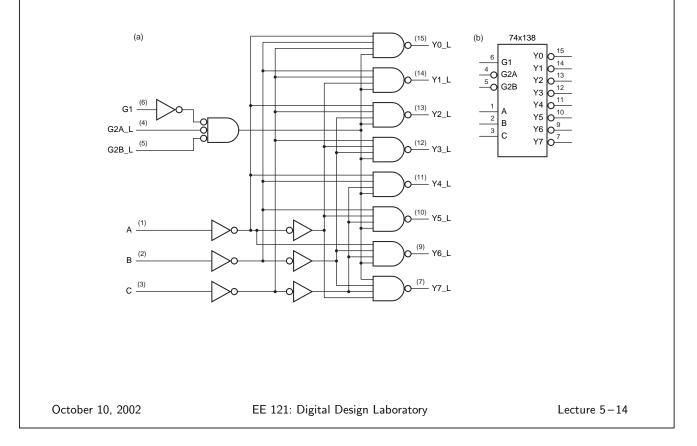

#### 74x138 3-to-8 decoder: symbol and schematic